|

Курсы и семинары :: Студенты и аспиранты Андреева А.Е. :: Публикации Андреева А.Е. :: Публикации учеников Андреева А.Е.

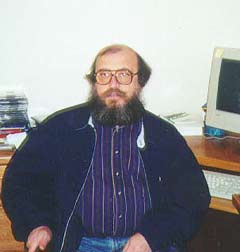

Андреев Александр Егорович

д.ф.м.н., профессор

Андреев Александр Егорович (13.07.1956, Пенза). Математик. Окончил механико-математический факультет МГУ (1978).

Кандидат физико-математических наук (1981), доктор физико-математических наук (1985).

Профессор кафедры математической теории интеллектуальных систем механико-математического факультета (1993). В Московском университете читает специальные курсы по теории сложности схем и алгоритмов.

Заместитель главного редактора журнала “Интеллектуальные системы”.

Область научных интересов. Дискретная математика, теория сложности схем и алгоритмов, распознавание образов. Первым построил пример булевской функции, которая имеет почти экспоненциальную сложность в классе монотонных схем из функциональных элементов, и тем самым решил проблему Шеннона, стоявшую более пятидесяти лет. Им разработан индустриальный метод оптимального синтеза самокорректирующихся схем для реализации булевских функций, исправляющий почти экспоненциальное число ошибок без увеличения асимптотической сложности. Им установлено, когда почти все матрицы имеют константное, полиномиальное и экспоненциально растущее число тестов и тупиковых тестов, каков информационный вес их признаков, какова длина их минимальных тестов. Им построены асимптотически оптимальные процедуры для построения важнейших семейств тестов. Им разработан градиентный метод поиска д.н.ф., близких к минимальным, для почти всех булевых функций. Этот метод имеет логарифмическую сложность по отношению к традиционно используемым.

Тема кандидатской диссертации: «О качественных и метрических свойствах тестовых алгоритмов». Тема докторской диссертации: «О синтезе функциональных сетей».

Подготовил 4 кандидатов наук. Опубликовал более 40 научных работ и более 100 патентов США по синтезу чипов.

См. также: http://istina.msu.ru/profile/aeandreev/

Список основных публикаций Андреева А.Е.

- Андреев А.Е., Гасанов Э.Э. , Кудрявцев В.Б. Теория тестового распознавания.

ФИЗМАТЛИТ, 2007, 320 с.

- Andreev A.E., Bolotov A.A. , Gribok S. Master controller architecture.

United States Patent N 7,308,633, December 11, 2007.

- Andreev A.E., Scepanovic R. System and method for efficiently testing a large random access memory space.

United States Patent N 7,305,597, December 4, 2007.

- Andreev A.E., Bolotov A.A., Scepanovic R. Memory mapping for parallel turbo decoding.

United States Patent N 7,305,593, December 4, 2007.

- Andreev A.E., Bolotov A.A. , Gribok S. RRAM communication system.

United States Patent N 7,283,385, October 16, 2007.

- Andreev A.E., Nikitin A.A., Vikhliantsev I.A. Digital gaussian noise simulator.

United States Patent N 7,263,470, August 28, 2007.

- Andreev A.E., Nikitin A.A. Method for optimizing execution time of parallel processor programs.

United States Patent N 7,257,807, August 14, 2007.

- Andreev A.E., Bolotov A.A., Pavisic I. Density driven layout for RRAM configuration module.

United States Patent N 7,246,337, July 17, 2007.

- Andreev A.E., Bolotov A.A., Scepanovic R. Search engine for large-width data.

United States Patent N 7,231,383, June 12, 2007.

- Andreev A.E., Bolotov A.A., Nikitin A.A. Process and apparatus for memory mapping.

United States Patent N 7,219,321, May 15, 2007.

- Andreev A.E., Bolotov A.A., Scepanovic R. Method and BIST architecture for fast memory testing in platform-based integrated circuit.

United States Patent N 7,216,278, May 8, 2007.

- Andreev A.E., Nikitin A.A., Vikhliantsev I.A. Process and apparatus for placing cells in an IC floorplan.

United States Patent N 7,210,113, April 24, 2007.

- Andreev A.E., Pavisic I., Vikhliantsev I.A. Memory tiling architecture.

United States Patent N 7,200,785, April 3, 2007.

- Andreev A.E., Nikitin A.A., Scepanovic R. RRAM memory timing learning tool.

United States Patent N 7,200,826, April 3, 2007.

- Andreev A.E., Bolotov A.A. Sequential tester for longest prefix search engines.

United States Patent N 7,200,785, April 3, 2007.

- Andreev A.E., Bolotov A.A., Pavisic I. Compact custom layout for RRAM column controller.

United States Patent N 7,194,717, March 20, 2007.

- Andreev A.E., Gashkov S.B., Nikitin A.A., Sedelev O.B. RRAM flipflop rcell memory generator.

United States Patent N 7,193,905, March 20, 2007.

- Andreev A.E., Bolotov A.A., Scepanovic R. FIFO memory with single port memory modules for allowing simultaneous read and write operations.

United States Patent N 7,181,563, February 20, 2007.

- Andreev A.E., Nikitin A.A., Scepanovic R. Yield driven memory placement system.

United States Patent N 7,168,052, January 23, 2007.

- Andreev A.E., Gashkov S.B. Method for constructing logic circuits of small depth and complexity for operation of inversion in finite fields of characteristic 2.

United States Patent N 7,167,886, January 23, 2007.

- Андреев А.Е., Кудрявцев В.Б. О сложности алгоритмов.

Интеллектуальные системы, т.10, 2006, Стр. 695-760.

- Андреев А.Е., Кудрявцев В.Б. Теория тестового распознавания.

Интеллектуальные системы, т.10, 2006, Стр. 95-140.

- Andreev A.E., Neznanov I.V., Nikitin A.A., Scepanovic R., Vikhliantsev I. Memory generation and placement.

United States Patent N 7,155,688, December 26, 2006.

- Andreev A.E., Nikitin A.A., Scepanovic R. Process and apparatus for fast assignment of objects to a rectangle.

United States Patent N 7,111,264, September 19, 2006.

- Andreev A.E., Nikitin A.A. Optimizing depths of circuits for Boolean functions.

United States Patent N 7,103,868, September 5, 2006.

- Andreev A.E., Scepanovic R., Vukovic V. Decomposer for parallel turbo decoding, process and integrated circuit.

United States Patent N 7,096,413, August 22, 2006.

- Andreev A.E., Ivanovic L., Pavisic I. Method and system for classifying an integrated circuit for optical proximity correction.

United States Patent N 7,093,228, August 15, 2006.

- Andreev A.E., Nikitin A.A. Method and apparatus of IC implementation based on C++ language description.

United States Patent N 7,082,593, July 25, 2006.

- Andreev A.E., Bolotov A.A., Radovanovic N. Built-in functional tester for search engines.

United States Patent N 7,082,561, July 25, 2006.

- Andreev A.E., Bolotov A.A., Vikhliantsev I.A. Integrated circuit and process for identifying minimum or maximum input value among plural inputs.

United States Patent N 7,072,922, July 4, 2006.

- Andreev A.E., Scepanovic R., Vikhliantsev I.A. Controller architecture for memory mapping.

United States Patent N 7,065,606, June 20, 2006.

- Andreev A.E., Bolotov A.A., Vikhliantsev I.A. Method for generating tech-library for logic function.

United States Patent N 7,062,726, June 13, 2006.

- Andreev A.E., Scepanovic R., Vikhliantsev I.A. Pseudo-random one-to-one circuit synthesis.

United States Patent N 7,050,582, May 23, 2006.

- Andreev A.E., Nikitin A.A. Decision function generator for a Viterbi decoder.

United States Patent N 7,039,855, May 2, 2006.

- Andreev A.E., Nikitin A.A., Vikhliantsev I.A. Process and apparatus for placement of cells in an IC during floorplan creation.

United States Patent N 7,036,102, April 25, 2006.

- Andreev A.E., Scepanovic R. FFS search and edit pipeline separation.

United States Patent N 7,035,844, April 25, 2006.

- Andreev A.E., Pavisic I., Scepanovic R., Vukovic V. RRAM backend flow.

United States Patent N 7,028,274, April 11, 2006.

- Andreev A.E., Scepanovic R. Table module compiler equivalent to ROM.

United States Patent N 7,003,510, February 21, 2006.

- Andreev A.E., Scepanovic R. Universal gates for ICs and transformation of netlists for their implementation.

United States Patent N 6,988,252, January 17, 2006.

- Andreev A.E., Pavisic I., Vikhliantsev I.A. Clock tree synthesis with skew for memory devices.

United States Patent N 6,941,533, September 6, 2005.

- Andreev A.E., Ivanovic L.D., Vikhliantsev I.A. Built-in test for multiple memory circuits.

United States Patent N 6,941,494, September 6, 2005.

- Andreev A.E., Scepanovic R. User selectable editing protocol for fast flexible search engine.

United States Patent N 6,941,314, September 6, 2005.

- Andreev A.E., Gashkov S.B., Lu A. Optimization of adder based circuit architecture.

United States Patent N 6,934,733, August 23, 2005.

- Andreev A.E., Nikitin A.A. Method for evaluating logic functions by logic circuits having optimized number of and/or switches.

United States Patent N 6,901,573, May 31, 2005.

- Andreev A.E., Andreev E.A., Bolotov A.A., Scepanovic R. Memory that allows simultaneous read requests.

United States Patent N 6,886,088, April 26, 2005.

- Andreev A.E., Vikhliantsev Igor. Netlist Redundancy Detection and Global Simplification

United States Patent N 6,848,094 , 1/25/2005

- Andreev A.E., Gasanov Elyar, Scepanovic Ranko. MULTIDIRECTIONAL ROUTER

United States Patent N 6,845,495 , 1/18/2005

- Andreev A.E., Scepanovic Ranko. Symbolic Simulation Driven Netlist Simplification

United States Patent N 6,842,750 , 1/11/2005

- Andreev A.E., Pavisic Ivan, Scepanovic Ranko. Process for Layout of Memory Matrices in Integrated Circuits

United States Patent N 6,804,811 , 10/12/2004

- Andreev A.E., Scepanovic Ranko. Method of Decreasing Instantaneous Current Without Affecting Timing

United States Patent N 6,795,954 , 9/21/2004

- Andreev A.E., Scepanovic Ranko. Prefix Comparator

United States Patent N 6,785,699 , 8/31/2004

- Andreev A.E., Pavisic Ivan, Scepanovic Ranko. Process Layout of Buffer Modules in Integrated Circuits

United States Patent N 6,760,896 , 7/6/2004

- Andreev A.E., Ivanovic Lav, Pavisic Ivan. Power Routing With Obstacles

United States Patent N 6,757,881 , 6/29/2004

- Andreev A.E., Scepanovic Ranko. Editing Protocol for Flexible Search Engines

United States Patent N 6,735,600, 5/11/2004

- Andreev A.E., Grinchuk Mikhail, Scepanovic Ranko . Process For Fast Cell Placement In Integrated Circuit Design

United States Patent N 6,704,915 , 3/9/2004

- Andreev A.E., Gashkov Sergei, Lu Aiguo. Optimization Of Comparator Architecture

United States Patent N 6,691,283, 2/10/2004

- Andreev A.E., Vukovic Vojislav. Spanning Tree Method for K-Dimensional Space

United States Patent N 6,665,850 , 12/16/2003

- Andreev A.E., Bolotov Anatoli, Scepanovic Ranko. Fast Free Memory Address Controller

United States Patent N 6,662,287 , 12/9/2003

- Andreev A.E., Andreev E.A., Pavisic I. Optimal clock timing schedule for an integrated circuit.

United States Patent N 6,615,397, September 2, 2003.

- Andreev A.E., Bolotov Anatoli, Scepanovic Ranko. Method and Apparatus for Formula Area and Delay Minimization

United States Patent N 6,587,990 , 7/1/2003

- Andreev A.E., Scepanovic Ranko. Fast Flexible Search Engine For Longest Prefix Match

United States Patent N 6,564,211 , 5/13/2003

- Andreev A.E., Scepanovic Ranko. Flexible Search Engine Having Sorted Binary Search Tree For Perfect Match

United States Patent N 6,553,370 , 4/22/2003

- Andreev A.E., Grinchuk M.I., Scepanovic R. Cell pin extensions for integrated circuits.

United States Patent N 6,536,027, March 18, 2003.

- Andreev A.E., Bolotov Anatoli, Scepanovic Ranko. Method And Apparatus for Locating Constants in Combinational Circuits

United States Patent N 6,536,016 , 3/18/2003

- Andreev A.E., Bolotov Anatoli, Scepanovic Ranko. Method and Apparatus for Detecting Equivalent and Anti-Equivalent Pins

United States Patent N 6,530,063 , 3/4/2003

- Andreev A.E., Pavisic Ivan, Scepanovic Ranko. Chip Core Size Estimation

United States Patent N 6,526,553, 2/25/2003

- Andreev A.E., Bolotov Anatoli, Pavisic Ivan. Method And Apparatus For Minimization of Net Delay By Optimal Buffer Insertion

United States Patent N 6,519,746 , 2/11/2003

- Andreev A.E., Bolotov Anatoli, Vikhliantsev Igor. Net Delay Optimization with Ramptime Violation Removal

United States Patent N 6,507,939 , 1/14/2003

- Andreev A.E., Bolotov Anatoli, Raspopovic Pedja. Channel Router with Buffer Insertion

United States Patent N 6,505,336, 1/7/2003

- Andreev A.E., Scepanovic Ranko. Process, Apparatus and Program for Transforming Program language Description of an IC to an RTL Description

United States Patent N 6,487,698 , 11/26/2002

- Andreev A.E., Ivanovic Lav, Scepanovic Ranko. e-Discrepant Self-Test Technique

United States Patent N 6,467,067 , 10/15/2002

- Andreev A.E., Bolotov Anatoli, Raspopovic Pedja. Process for Solving Assignment Problems in Integrated Circuit Designs with Unimodal Object Penalty Functions and Linearly Ordered Set of Boxes

United States Patent N 6,453,453, 9/17/2002

- Andreev A.E., Pavisic Ivan, Raspopovic Pedja. Wire Routing Optimization

United States Patent N 6,412,102 , 6/25/2002

- Aleshin S.V., Andreev A.E., Jones E.R., Kapoor A.K., Koford J.S., Kudryavtsev V.B., Padmanahben G.R., Podkolzin A.S., Rostoker M.D., Scepanovic R. Hexagonal architecture.

United States Patent N 6,407,434, June 18, 2002.

- Andreev A.E., Gasanov E.E., Raspopovic P., Scepanovic R. Method and apparatus for parallel simultaneous global and detail routing.

United States Patent N 6,324,674, November 27, 2001.

- Aleshin S.V., Andreev A.E., Jones E.R., Kapoor A.K., Koford J.S., Kudryavtsev V.B., Padmanahben G.R., Podkolzin A.S., Rostoker M.D., Scepanovic R. Programmable triangular shaped device having variable gain.

United States Patent N 6,312,980, November 6, 2001.

- Andreev A.E., Jones E., Koford J.S., Pavisic I., Scepanovic R. Advanced modular cell placement system.

United States Patent N 6,292,929, September 18, 2001.

- Andreev A.E., Bolotov Anatoli, Pavisic Ivan, Scepanovic Ranko. Modifying Timing Graph To Avoid Given Set Of Paths

United States Patent N 6,292,924 , 9/18/2001

- Andreev A.E., Raspopovic P., Scepanovic R. Method and apparatus for local optimization of the global routing.

United States Patent N 6,289,495, September 11, 2001.

- Andreev A.E., Raspopovic P., Scepanovic R. Method and apparatus for coarse global routing.

United States Patent N 6,260,183, July 10, 2001.

- Andreev A.E., Gasanov Elyar, Raspopovic Pedja, Scepanovic Ranko. NET ROUTING USING BASIS ELEMENT DECOMPOSITION

United States Patent N 6,253,363 , 6/26/2001

- Andreev A.E., Raspopovic P., Scepanovic R. Method and apparatus for parallel Steiner tree routing.

United States Patent N 6,247,167, June 12, 2001.

- Andreev A.E., Raspopovic Pedja, Scepanovic Ranko. Method And Apparatus For Minimization Of Process Defects While Routing

United States Patent N 6,230,306 , 5/8/2001

- Andreev A.E., Koford J.S., Scepanovic R. Advanced modular cell placement system with overlap remover with minimal noise.

United States Patent N 6,223,332, April 24, 2001.

- Andreev A.E., Pavisic Ivan, Scepanovic Ranko. Method And Apparatus For Determining Wire Routing

United States Patent N 6,186,676 , 2/13/2001

- Andreev A.E., Pavisic Ivan, Raspopovic Pedja. Metal Layer Assignment

United States Patent N 6,182,272 , 1/30/2001

- Andreev A.E., Gasanov Elyar, Raspopovic Pedja, Scepanovic Ranko. Method And Apparatus For Hierarchical Global Routing Descend.

United States Patent N 6,175,950 , 1/16/2001

- Andreev A.E., Raspopovic Pedja, Scepanovic Ranko. Memory-Saving Method And Apparatus For Partitioning High Fanout Nets.

United States Patent N 6,154,874 , 11/28/2000

- Aleshin S.V., Andreev A.E., Koford J.S., Kudryavtsev V.B., Podkolzin A.S., Scepanovic R. Physical design automation system and process for designing integrated circuit chips using multiway partitioning with constraints.

United States Patent N 6,134,702, October 17, 2000.

- Andreev A.E., Pavisic I., Scepanovic R. Method and apparatus for horizontal congestion removal.

United States Patent N 6,123,736, September 26, 2000.

- Aleshin S.V., Andreev A.E., Jones E.R., Kapoor A.K., Koford J.S., Kudryavtsev V.B., Padmanahben G.R., Podkolzin A.S., Rostoker M.D., Scepanovic R. Triangular semiconductor or gate.

United States Patent N 6,097,073, August 1, 2000.

- Andreev A.E., Koford James S., Scepanovic Ranko. Advanced Modular Cell Placement System With Sinusoidal Optimization

United States Patent N 6,085,032 , 7/4/2000

- Andreev A.E., Pavisic I., Scepanovic R. Method and apparatus for continuous column density optimization.

United States Patent N 6,075,933, June 13, 2000.

- Andreev A.E., Pavisic I., Scepanovic R. Method and apparatus for congestion driven placement.

United States Patent N 6,070,108, May 30, 2000.

- Andreev A.E., Pavisic Ivan, Scepanovic Ranko. Method And Apparatus For Congestion Removal

United States Patent N 6,068,662 , 5/30/2000

- Andreev A.E., Jones E., Koford J.S., Pavisic I., Scepanovic R. Advanced modular cell placement system.

United States Patent N 6,067,409, May 23, 2000.

- Andreev A.E., Pavisic I., Scepanovic R. Method and apparatus for vertical congestion removal.

United States Patent N 6,058,254, May 2, 2000.

- Andreev A.E., Koford J, Pavisic I., S., Scepanovic R. Physical design automation system and process for designing integrated circuit chip using "chessboard" and "jiggle" optimization.

United States Patent N 6,038,385, March 14, 2000.

- Andreev A.E., Koford James S., Scepanovic Ranko. Advanced Modular Cell Placement System With Median Control And Increase In Resolution

United States Patent N 6,030,110 , 2/29/2000

- Andreev A.E., Koford James S., Scepanovic Ranko. Advanced Modular Cell Placement System With Overlap Remover With Minimal Noise.

United States Patent N 6,026,223 , 2/15/2000

- Andreev A.E., Pavisic Ivan, Scepanovic Ranko. Parallel Processing of Integrated Circuit Pin Arrival Times

United States Patent N 6,000,038 , 12/7/1999

- Aleshin S.V., Andreev A.E., Jones E.R., Kapoor A.K., Koford J.S., Kudryavtsev V.B., Padmanahben G.R., Podkolzin A.S., Rostoker M.D., Scepanovic R. Architecture having diamond shaped or parallelogram shaped cells.

United States Patent N 5,973,376, October 26, 1999.

- Andreev A.E., Koford James S., Scepanovic Ranko. Advanced Modular Cell Placement System With Optimization Of Cell Neighborhood System.

United States Patent N 5,971,588 , 10/26/1999.

- Andreev A.E., Koford James S., Scepanovic Ranko. Advanced Modular Cell Placement System With Functional Sieve Optimization Technique .

United States Patent N 5,963,455 , 10/5/1999

- Andreev A.E., Jones E., Scepanovic R. Parallel processor implementation of net routing.

United States Patent N 5,930,500, July 27, 1999.

- Andreev A.E., Koford James S., Scepanovic Ranko. Advanced Modular Cell Placement System With Coarse Overflow Remover.

United States Patent N 5,914,888 , 6/22/1999.

- Aleshin S.V., Andreev A.E., Koford J.S., Kudryavtsev V.B., Podkolzin A.S., Roseboom E.M., Scepanovic R. Physical design automation system and process for designing integrated circuit chips using highly parallel sieve optimization with multiple "jiggles".

United States Patent N 5,909,376, June 1, 1999.

- Andreev A.E., Pavisic I., Scepanovic R. Integrated circuit floor plan optimization system.

United States Patent N 5,898,597, April 27, 1999.

- Andreev A.E., Koford James S., Scepanovic Ranko. Advanced Modular Cell Placement System With Iterative One Dimensional Preplacement Optimization

United States Patent N 5,892,688 , 4/6/1999

- Aleshin S.V., Andreev A.E., Jones E.R., Kapoor A.K., Koford J.S., Kudryavtsev V.B., Padmanahben G.R., Podkolzin A.S., Rostoker M.D., Scepanovic R. Tri-directional interconnect architecture for SRAM.

United States Patent N 5,889,329, March 30, 1999.

- Andreev A.E., Pavisic I., Scepanovic R. Integrated circuit cell placement parallelization with minimal number of conflicts.

United States Patent N 5,875,118, February 23, 1999.

- Andreev A.E., Koford J.S., Scepanovic R. Advanced modular cell placement system.

United States Patent N 5,872,718, February 16, 1999.

- Aleshin S.V., Andreev A.E., Jones E.R., Kapoor A.K., Koford J.S., Kudryavtsev V.B., Padmanahben G.R., Podkolzin A.S., Rostoker M.D., Scepanovic R. Hexagonal sense cell architecture.

United States Patent N 5,872,380, February 16, 1999.

- Andreev A.E., Koford James S., Scepanovic Ranko. Advanced Modular Cell Placement System With Dispersion-Driven Levelizing System

United States Patent N 5,870,312 , 2/9/1999

- Andreev A.E., Koford James S., Scepanovic Ranko. Advanced Modular Cell Placement System With Fast Procedure For Finding A Levelizing Cut Point

United States Patent N 5,870,311 , 2/9/1999

- Andreev A.E., Koford James S., Scepanovic Ranko. Advanced Modular Cell Placement System With Density Driven Capacity Penalty System

United States Patent N 5,867,398 , 2/2/1999

- Aleshin S.V., Andreev A.E., Jones E.R., Kapoor A.K., Koford J.S., Kudryavtsev V.B., Padmanahben G.R., Podkolzin A.S., Rostoker M.D., Scepanovic R. Triangular semiconductor NAND gate.

United States Patent N 5,864,165, January 26, 1999.

- Andreev A.E., Pavisic I., Scepanovic R. Efficient multiprocessing for cell placement of integrated circuits.

United States Patent N 5,859,782, January 12, 1999.

- Andreev A.E., Koford James S., Scepanovic Ranko. Advanced Modular Cell Placement System With Affinity Driven Discrete Placement Optimization

United States Patent N 5,844,811 , 12/1/1998

- Aleshin S.V., Andreev A.E., Koford J.S., Kudryavtsev V.B., Podkolzin A.S., Scepanovic R. Physical design automation system and method using monotonically improving linear clusterization.

United States Patent N 5,838,585, November 17, 1998.

- Andreev A.E., Koford James S., Scepanovic Ranko. Advanced Modular Cell Placement System With Minimizing Maximal Cut Driven Affinity System

United States Patent N 5,835,381 , 11/10/1998

- Aleshin S.V., Andreev A.E., Boyle D.B., Koford J.S., Kudryavtsev V.B., Podkolzin A.S., Scepanovic R. Computer implemented method for leveling interconnect wiring density in a cell placement for an integrated circuit chip

United States Patent N 5,835,378, November 10, 1998.

- Aleshin S.V., Andreev A.E., Jones E.R., Kapoor A.K., Koford J.S., Kudryavtsev V.B., Padmanahben G.R., Podkolzin A.S., Rostoker M.D., Scepanovic R. Triangular semiconductor "AND" gate device.

United States Patent N 5,834,821, November 10, 1998.

- Andreev A.E., Koford James S., Scepanovic Ranko. Advanced Modular Cell Placement System With Wire Length Driven Affinity System

United States Patent N 5,831,863 , 11/3/1998

- Aleshin S.V., Andreev A.E., Jones E.R., Kapoor A.K., Koford J.S., Kudryavtsev V.B., Padmanahben G.R., Podkolzin A.S., Rostoker M.D., Scepanovic R. CAD for hexagonal architecture.

United States Patent N 5,822,214, October 13, 1998.

- Andreev A.E., Koford James S., Scepanovic Ranko. Advanced Modular Cell Placement System With Neighborhood System Driven Optimization

United States Patent N 5,812,740 , 9/22/1998

- Aleshin S.V., Andreev A.E., Jones E.R., Kapoor A.K., Koford J.S., Kudryavtsev V.B., Padmanahben G.R., Podkolzin A.S., Rostoker M.D., Scepanovic R. Transistors having dynamically adjustable characteristics.

United States Patent N 5,811,863, September 22, 1998.

- Andreev A.E., Andreev A.E., Koford J.S., Scepanovic R. Advanced modular cell placement system with cell placement crystallization.

United States Patent N 5,808,899, September 15, 1998.

- Aleshin S.V., Andreev A.E., Jones E.R., Kapoor A.K., Koford J.S., Kudryavtsev V.B., Padmanahben G.R., Podkolzin A.S., Rostoker M.D., Scepanovic R. Polydirectional non-orthoginal three layer interconnect architecture.

United States Patent N 5,808,330, September 15, 1998.

- Aleshin S.V., Andreev A.E., Jones E.R., Kapoor A.K., Koford J.S., Kudryavtsev V.B., Padmanahben G.R., Podkolzin A.S., Rostoker M.D., Scepanovic R. Hexagonal SRAM architecture.

United States Patent N 5,801,422, September 1, 1998.

- Andreev A.E., Koford J.S., Pavisic I., Scepanovic R. Physical design automation system and process for designing integrated circuit chip using simulated annealing with "chessboard and jiggle" optimization.

United States Patent N 5,796,625, August 18, 1998.

- Aleshin S.V., Andreev A.E., Jones E.R., Kapoor A.K., Koford J.S., Kudryavtsev V.B., Padmanahben G.R., Podkolzin A.S., Rostoker M.D., Scepanovic R. Hexagonal architecture with triangular shaped cells.

United States Patent N 5,789,770, August 4, 1998.

- Aleshin S.V., Andreev A.E., Jones E.R., Koford J.S., Kudryavtsev V.B., Podkolzin A.S., Scepanovic R. Physical design automation system and process for designing integrated circuit chips using generalized assignment.

United States Patent N 5,784,287, July 21, 1998.

- Aleshin S.V., Andreev A.E., Jones E.R., Kapoor A.K., Koford J.S., Kudryavtsev V.B., Padmanahben G.R., Podkolzin A.S., Rostoker M.D., Scepanovic R. Hexagonal field programmable gate array architecture.

United States Patent N 5,777,360, July 7, 1998.

- Aleshin S.V., Andreev A.E., Jones E.R., Kapoor A.K., Koford J.S., Kudryavtsev V.B., Padmanahben G.R., Podkolzin A.S., Rostoker M.D., Scepanovic R. Hexagonal DRAM array.

United States Patent N 5,742,086, April 21, 1998.

- Aleshin S.V., Andreev A.E., Koford J.S., Kudryvavtsev V.B., Podkolzin A.S., Roseboom E.M., Scepanovic R. Physical design automation system and process for designing integrated circuit chips using fuzzy cell clusterization.

United States Patent N 5,712,793, January 27, 1998.

- Aleshin Stanislav, Andreev A.E., Koford James S., Kudryavtsev Valeri, Podkolzin Alexander, Scepanovic Ranko. Physical Design Automation System And Process For Designing Integrated Circuit Chips Multiway Partitioning With Constraints

United States Patent N 5,699,265 , 12/16/1997

- Aleshin Stanislav, Andreev A.E., Koford James S., Kudryavtsev Valeri, Podkolzin Alexander, Scepanovic Ranko. Physical Design Automation System And Method Using Hierarchical Clusterization And Placement Improvement Based On Complete Replacement Of Cell Clusters

United States Patent N 5,661,663 , 8/26/1997

- Aleshin S.V., Andreev A.E., Jones E.R., Kapoor A.K., Koford J.S., Kudryavtsev V.B., Padmanahben G.R., Podkolzin A.S., Rostoker M.D., Scepanovic R. Microelectronic integrated circuit including triangular semiconductor "or" gate.

United States Patent N 5,654,563, August 5, 1997.

- Aleshin S.V., Andreev A.E., Jones E.R., Kapoor A.K., Koford J.S., Kudryavtsev V.B., Padmanahben G.R., Podkolzin A.S., Rostoker M.D., Scepanovic R. Microelectronic integrated circuit including triangular CMOS "nand" gate device.

United States Patent N 5,650,653, July 22, 1997.

- Aleshin S.V., Andreev A.E., Jones E.R., Kapoor A.K., Koford J.S., Kudryavtsev V.B., Padmanahben G.R., Podkolzin A.S., Rostoker M.D., Scepanovic R. Physical Design Automation System And Method Using Hierarchical

United States Patent N 5,631,581, May 20, 1997.

- Andreev A.E., Clementi A.E.F., Penna P., Rolim J.D.P. Parallel Read Operations Without Memory Contention

Electronic Colloquium on Computational Complexity (ECCC) 7(53): (2000)

- Andreev A.E., Clementi A.E.F., Rolim J.D.P. Worst-Case Hardness Suffices for Derandomization: A New Method for Hardness-Randomness Trade-offs.

Theor. Comput. Sci. 221(1-2) (1999) pp. 3-18

- Andreev A.E., Clementi A.E.F., Rolim J.D.P., Trevisan L. Weak Random Sources, Hitting Sets, and BPP Simulations.

SIAM J. Comput. 28(6) (1999) pp. 2103-2116

- Andreev A.E., Clementi A.E.F., Penna P., Rolim J.D.P. Memory Organization Schemes for Large Shared Data: A Randomized Solution for Distributed Memory Machines.

STACS 1999 pp. 68-77

- Andreev A.E., Baskakov J.L., Clementi A.E.F., Rolim J.D.P. Small Pseudo-Random Sets Yield Hard Functions: New Tight Explict Lower Bounds for Branching Programs.

ICALP 1999 pp. 179-189

- Andreev A.E., Clementi A.E.F., Rolim J.D.P. A New General Derandomization Method.

J. ACM 45(1) (1998) pp. 179-213

- Андреев А.Е., Болотов А.А., Коляда К.В., Фролов А.Б. Прикладные задачи дискретной математики и сложность алгоритмов.

Изд-во МЭИ, М., 1997, 310 с.

- Andreev A.E., Soloviev S. A Deciding Algorithm for Linear Isomorphism of Types with Complexity O (n log2(n)).

Category Theory and Computer Science 1997 pp. 197-209

- Andreev A.E., Clementi A.E.F., Crescenzi P., Dahlhaus E., De Agostino S., Rolim J.D.P. The Parallel Complexity of Approximating the High Degree Subgraph Problem.

Theor. Comput. Sci. 205(1-2): (1998) 1997 pp. 261-282

- Andreev A.E., Clementi A.E.F., Rolim J.D.P. Weak Random Sources, Hitting Sets, and BPP Simulations,

In Proceedings of the 38th IEEE Symposium on Foundations of Computer Science, 1997. p.264-273

- Andreev A.E., Clementi A.E.F., Rolim J.D.P. Optimal bounds for the approximation of boolean functions and some applications

Theoretical Computer Science (Elsevier Science) Volume 180, Issue 1-2, 1997, p. 243-268.

- Andreev A.E., Clementi A.E.F., Rolim J.D.P. Worst-Case Hardness Suffices for Derandomization:

A New Method for Hardness-Randomness Trade-offs. ICALP 97, Lecture Notes in Computer Science, 1256, p.177-187.

- Andreev A.E., Clementi A.E.F., Rolim J.D.P. Efficient Constructions of Hitting Sets for Systems of Linear Functions STACS 97,

Lecture Notes in Computer Science, 1200, p.387-398.

- Andreev A.E., Clementi A.E.F., Rolim J.D.P. Constructing the highest subgraph for dense graphs is in NCAL

Theoretical Computer Science (Elsevier Science) Volume 166 Issue 1-2, 1996, p. 12.

- Andreev A.E., Clementi A.E.F., Rolim J.D.P. Constructing the highest degree subgraph for dense graphs is in NCAS

Theoretical Computer Science (Elsevier Science) Volume 161, Issue 1-2, 1996, p. 307-314.

- Andreev A.E. On the parallel computation of boolean functions on unrelated inputs,

in Proc. of 4-th Israeli Symposium on Theory of Computing and Systems (ISTCS'96), 1996.

- Andreev A.E., Clementi A., Rolim J. Hitting sets derandomize BPP,

ICALP 96, Lecture Notes in Computer Science, 1099, 1996 p.357-368.

- Andreev A.E., Clementi A., Rolim J. Optimal Bounds on the Approximation of Boolean Functions, with Consequences on the Concept of Hardness,

XIII Annual Symposium on Theoretical Aspects of Computer Science (STACS'96), Lecture Notes in Computer Science, 1046, p.319-329.

- Andreev A.E., Clementi A.E.F., Crescenzi P., De Agostino S. , Dhalhaus E., Rolim J.D.P. The parallel complexity of approximating the high degree subgraph problem,

in VI Annual International Symposium on Algorithms and Computation (ISAAC'95), Lecture Notes in Computer Science, Springer-Verlag, Cairns (Australia), (1995).

- Andreev A.E., Clementi A.E.F., Rolim J.D.P. Constructing the highest degree subgraph problem for dense graphs is in NCAS,

International Conference on High Performance Computing (HiPC'95), New Dehli (India) (1995).

- Andreev A.E. Complexity of nondetetermenistic functions.

University of Aarhus, BRICS Report Series, RS-94-2, 1994. p.1-47

- Андреев А.Е., Часовских A.A. Автоматная сложность формул в базисах из двувходовых элементов

Дискретная математика, T 8, N 4, 1996. p.123-133

- Андреев А.Е., Вихлянцев И.A. О сложности нумерации

Дискретная математика, T 8, N 4, 1996. p.44-56

- Андреев А.Е., Часовских A.A. Сложность автоматов для вычисления формул.

Вестник Московского Университета 1996, N 4, p.22-24.

- Андреев А.Е., Вихлянцев И.А. Оценки длины кода для схем из функциональных элементов.

Дискретная математика, T 6, N 4, 1994. p.10-20

- Андреев А.Е. Почти оптимальное протыкающее множество.

Доклады РАН, v.340, N 4, 1995. p.453-455

- Андреев А.Е. Об одном методе синтеза формул.

Вестник Московского университета, N 6, 1994. p.23-27

- Андреев А.Е. Сложность и кодирование булевых функций.

Доклады РАН, т.331, N 5, 1993. с.533-535

- Андреев А.Е. О сложности градиентных вентильных схем.

Дискретная математика, v.7, is.1, 1995. p.66-76

- Andreev A.E. Complexity of graduent's gating curcuits.

Dagstul-Seminar Report; 45 23. – 28.8.92 (9235), 1992. p.5

- Andreev A.E. On an algebraic method for constraction of extremal Boolean matrices.

Computer and Artificial Intelligence v.10,N 2, 1991. p.99-109

- Андреев А.Е. Частичные булевы функции и сложность.

Тезисы докладов 9-ой Всесоюзной конференции по проблемам теоретической кибернетики. г.Волгоград,1990 г., стр.35-41.

- Андреев А.Е. О сложности реализации частичных булевых функций схемами из функциональных элементов.

Дискретная математика,1989,т.1,вып.4, стр.36-45.

- Андреев А.Е., Болотов А.А., Строгалов А.С. , Фролов А.Б. Прикладные задачи дискретной математики в энергетике.

Учебное пособие по курсу дискретной математики, изд. МЭИ, 1988, 92 с.

- Андреев А.Е. Частичные булевы функции и эффективные нижние оценки.

Тезисы докладов 8-ой Всесоюзной конференции по проблемам теоретической кибернетики. г.Горький, 1988 г., стр.23-24.

- Андреев А.Е. О синтезе схем из функциональных элементов в полных монотонных базисах.

Наука,Математические вопросы кибернетики, 1988, N 1, стр.114-139.

- Андреев А.Е. Об одном методе получения более чем квадратичных эффективных нижних оценок сложности схем.

Вестник Московского университета,1987,N 1, стр.70-73.

- Андреев А.Е. О сложности реализации недоопределенных булевых матриц вентильными схемами.

Математические заметки,1987,N 1, стр.77-86.

- Андреев А.Е. Об одном методе получения эффективных нижних оценок монотонной сложности.

Алгебра и логика, 1987,N 1, стр.3-26.

- Андреев А.Е. Эффективные нижние оценки сложности некоторых типов схем.

"Шпрингер",Труды 6-ой Международной конференции "Основы теории вычислений",1987., стр.24-29.

- Андреев А.Е. О метрических свойствах модельных многоэкстремальных комбинаторно-логических задач.

Саратовский ГУ, сб.Теоретические проблемы кибернетики, 1986, стр.14-18.

- Андреев А.Е. Об одном семействе булевых матриц.

Вестник Московского университета,1986, N 2, стр.97-100.

- Андреев А.Е. О продолжении пар таблиц без изменения системы тестов.

Саратовский ГУ,Методыи системы технической диагностики, 1985, стр.13-20.

- Андреев А.Е. О сложности реализации вентильными схемами транзитивных отношений.

МЭИ, сб.Физическое и математическое моделирование дискретных систем,1985, стр.11-21.

- Андреев А.Е. О синтезе топологических функциональных сетей.

ИПМех АН СССР,1985, препринт, N 249. стр.1-67.

- Андреев А.Е. Об одном методе получения нижних оценок сложности индивидуальных монотонных функций.

ИПМех АН СССР,1985, препринт, N 248. стр.1-15.

- Андреев А.Е. О синтезе контактных многополюсников.

Тезисы докладов 7-ой Всесоюзной конференции по проблемам теоретической кибернетики. г.Иркутск,1985 стр.9-10.

- Андреев А.Е. О сложности монотонных функций.

Вестник Московского университета, 1985,N 4, стр.83-87.

- Андреев А.Е. Об одной модификации градиентного алгоритма.

Вестник Московского университета, 1985, N 3, стр.29-35.

- Андреев А.Е. О числе максимальных интервалов.

Вестник Московского университета, 1985, N 2 стр.13-16.

- Андреев А.Е. Универсальный принцип самокорректирования.

Математический сборник,1985,т.127(169) N 6 , стр.147-172.

- Андреев А.Е. Об одном методе получения нижних оценок сложности индивидуальных монотонных функций.

Доклады АН СССР 1985,т.281,N 2, стр.1033-1037.

- Андреев А.Е. Метод бесповторной редукции синтеза самокорректирующихся схем.

Доклады АН СССР 1985, т.283, N 2, стр.265-269.

- Андреев А.Е. Об асимптотическом поведении числа тупиковых тестов и длины минимального теста для почти всех таблиц.

Наука, Проблемы кибернетики, 1984 г. стр.117-141.

- Андреев А.Е. О синтезе самокорректирующихся управляющих систем.

Доклады АН СССР 1984, т.277, N 3, стр.521-525.

- Андреев А.Е. К проблеме минимизации дизьюнктивных нормальных форм.

Доклады АН СССР 1984, т.274, N 2, стр.265-269.

- Андреев А.Е. О синтезе дизьюнктивных нормальных форм.

Доклады АН СССР 1983, т.269, N 1, стр.11-15.

- Андреев А.Е. О сложности дизьюнктивных нормальных форм.

Тезисы докладов 6-ой Всесоюзной конференции по математической логике. г.Тбилиси, 1982 стр.6-6.

- Андреев А.Е. О сложности проверки набора столбцов на тестовость.

МГУ, сб. Прикладная математика и математическое обеспечение ЭВМ, 1981. стр.91-91.

- Андреев А.Е. О восстановлении пар таблиц по их системам тестов.

ВЦ АН СССР, сб. работ по математической кибернетики, 1981. стр.3-19.

- Андреев А.Е. О свойстве продолжаемости пар бинарных таблиц.

МГУ, сб. Некоторые вопросы математики и механики, 1981. стр.23-25.

- Андреев А.Е. О тупиковых и минимальных тестах.

Доклады АН СССР 1981, т.256, N 3, стр.521-524.

- Андреев А.Е. Об одном классе алгоритмов построения тупиковых тестов.

Тезисы докладов 5-ой Всесоюзной конференции по проблемам теоретической кибернетики. г.Новосибирск, 1980 стр.189-191.

- Андреев А.Е. Некоторые вопросы распознавания образов.

Доклады АН СССР 1980,т.225,N 4, стр.781-784.

- Андреев А.Е. О восстановлении пар таблиц по их системам тестов.

Тезисы докладов 4-ой Всесоюзной конференции по проблемам теоретической кибернетики. г.Новосибирск, 1977 стр.192-193.

Список научных публикаций учеников Андреева А.Е.

Наверх

|